# Simple Noise Deembedding Technique for On-Wafer Shield-Based Test Fixtures

Troels Emil Kolding, *Member, IEEE*, and Christian Rye Iversen

**Abstract**—Conventional on-wafer test fixtures have a significant impact on two-port noise-parameter measurements of silicon devices at gigahertz frequencies. This leads to increased measuring inaccuracy, as well as a need for complicated and area-consuming deembedding procedures. Alternatively, shield-based test fixtures are characterized by very few series effects and, thus, support cost-efficient and simple deembedding. The applicability of a simple one-step method is illustrated with experimental data. A performance comparison is made to full-scale deembedding methods based on conventional, as well as shield-based test fixtures.

**Index Terms**—Integrated circuits, microwave measurements, semiconductor device noise.

## I. INTRODUCTION

WITH THE increased application of silicon technology for RF applications, microwave characterization of MOS-FETs and bipolar junction transistors (BJTs) has become an important sales parameter for the semiconductor industry; even to those foundries that used to concentrate on digital and low-frequency analog applications. To decrease cost and complexity of device characterization, it is important that simple, yet accurate, measuring approaches become available. In a previous publication [1], it was shown that the use of shield-based on-wafer test fixtures greatly improves the accuracy, as well as the convenience of scattering-parameter measurements. In this paper, we will demonstrate that such test fixtures are also highly applicable to high-frequency noise-parameter measurements.

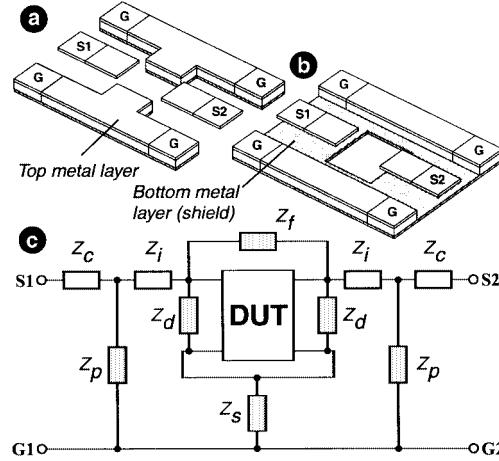

Conventional test fixtures, as shown in Fig. 1(a), may be characterized by the equivalent test-fixture model shown in Fig. 1(c) [2]. The resistive loss of substrate and series interconnects gives a large discrepancy between raw noise measurements and the actual noise parameters of the device-under-test (DUT). The equivalent series resistance of the parallel effects of conventional test fixtures ( $\Re\{Z_p\}$  and  $\Re\{Z_d\}$ ) is often very high; typically 20–100  $\Omega$ . This may lead to a significant offset between minimum noise figure  $NF_{min}$  and equivalent noise resistance  $R_n$  between the actual DUT and the DUT measured in a test fixture [3], [4]. Shield-based test fixtures, as shown in Fig. 1(b), have been introduced to reduce the resistive losses of dangling leg straps ( $Z_s$ ), as well as the coupling parameters  $Z_p$ ,  $Z_d$ , and  $Z_f$  [1]. The resistive part of the parallel components is typically below 1  $\Omega$  for shield-based implementations, whereas the

Fig. 1. Illustration of: (a) conventional test fixture, (b) shield-based test fixture, and (c) full-scale equivalent model for fixture parasitics.

noise contribution of the test fixture is often low enough to be neglected in comparison to the DUT noise. These considerations allow us to propose and test a simple measuring approach based on shield-based fixtures. In this paper, we will compare a full-scale deembedding (FSD) approach to this simple method in terms of accuracy. As a means of verification, we use measurements of devices and test structures fabricated in a submicrometer CMOS technology.

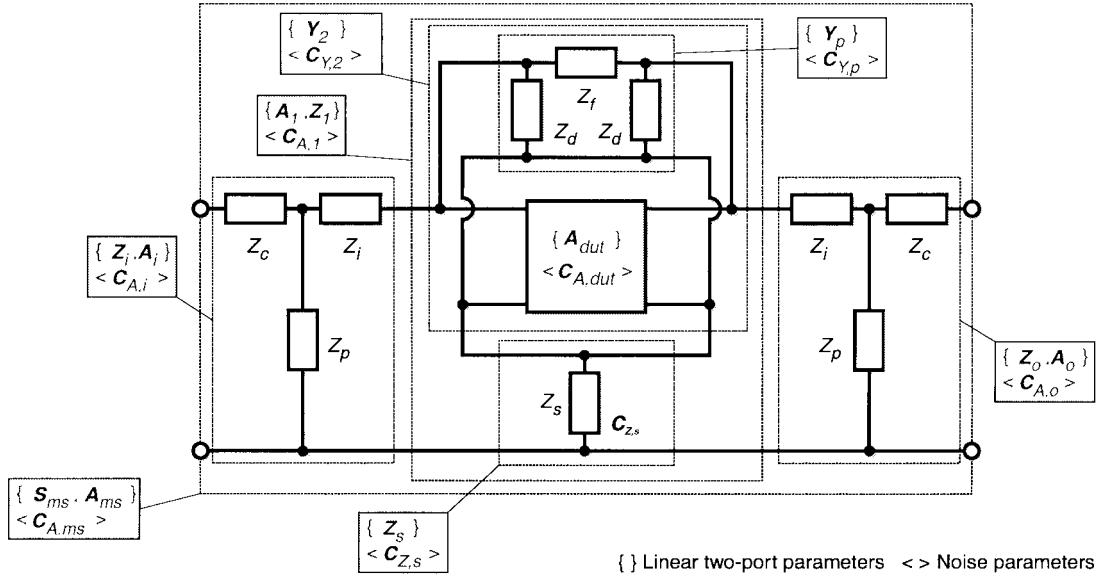

## II. FSD

The traditional deembedding of noise measurements is based on noise correlation matrices, as proposed by Hillbrand and Russer [5]. The procedure goes through: 1) identification of parasitics and 2) subtraction of these using either cascade, admittance, or impedance representations. The method has been generalized in several references, including [4] and [6]. When using the full-scale equivalent test-fixture model shown in Fig. 1(c), the method becomes quite involved and several on-wafer test structures are required in order to conduct the parasitics extraction. A division of the test-fixture model into convenient parameter groups is depicted in Fig. 2.

We may assume that all model parameters have been determined from an extraction method such as the one presented in [2]. From the total measured noise parameters for the DUT with the test fixture ( $R'_n$ ,  $F'_{min}$ , and  $Y'_{SOF}$ ), we extract the total cascade correlation matrix as [6]

$$C_{A,ms} = 2kT_0 \begin{bmatrix} R'_n & \psi^* \\ \psi & R'_n |Y'_{SOF}|^2 \end{bmatrix} \quad (1)$$

Manuscript received November 1, 2000; revised February 4, 2002.

T. E. Kolding is with Nokia Networks, DK-9220 Aalborg, Denmark (e-mail: troels.kolding@nokia.com).

C. R. Iversen is with RF Micro Devices, DK-9400 Nørresundby, Denmark (e-mail: civersen@rfmd.com).

Digital Object Identifier 10.1109/TMTT.2002.806938

Fig. 2. Redrawn full-scale test-fixture model suitable for noise deembedding. The model is divided into smaller two-port networks that are each characterized by linear two-port parameters, as well as noise correlation matrices.

where

$$\psi = \frac{1}{2} (F'_{\min} - 1) - R'_n Y'_{\text{SOF}} \quad (2)$$

and  $T_0$  is the standard noise temperature. To simplify the notation, we assume that the noise parameters implicitly refer to the actual noise temperature  $T_f$  of the DUT and test fixture. The deembedding procedure starts out by determining the cascade matrix correlation matrices for the input and the output as

$$C_{A,i} = 2kT_f \mathbf{X}_i \Re\{\mathbf{Z}_i\} \mathbf{X}_i^\dagger, \quad \mathbf{X}_i = \begin{bmatrix} 1 & -1 - \frac{Z_c}{Z_p} \\ 0 & -\frac{1}{Z_p} \end{bmatrix} \quad (3)$$

$$C_{A,o} = 2kT_f \mathbf{X}_o \Re\{\mathbf{Z}_o\} \mathbf{X}_o^\dagger, \quad \mathbf{X}_o = \begin{bmatrix} 1 & -1 - \frac{Z_i}{Z_p} \\ 0 & -\frac{1}{Z_p} \end{bmatrix} \quad (4)$$

where “ $\dagger$ ” denotes the Hermitian adjoint or complex conjugate transpose given as  $\mathbf{A}^\dagger = (\mathbf{A}^T)^*$  [7]. The matrices  $\mathbf{A}_i$  and  $\mathbf{A}_o$  can be found using lookup tables found in most microwave textbooks, e.g., [8]. With reference to Fig. 2, we determine the inner cascade correlation matrix as

$$C_{A,1} = \mathbf{A}_i^{-1} (C_{A,ms} - C_{A,i}) (\mathbf{A}_i^\dagger)^{-1} - \mathbf{A}_1 \mathbf{C}_{A,o} \mathbf{A}_1^\dagger. \quad (5)$$

The  $ABCD$  two-port matrix  $\mathbf{A}_1$  is determined from the measured parameters as

$$\mathbf{A}_1 = \mathbf{A}_i^{-1} \mathbf{A}_{ms} \mathbf{A}_o^{-1} \quad (6)$$

whereas the input and output two-ports have been removed. To continue the deembedding of  $Z_s$ ,  $Z_d$ , and  $Z_f$ , the admittance

noise correlation matrix is determined as

$$C_{Y,2} = Y_2 (C_{Z,1} - 2kT_f \Re\{\mathbf{Z}_s\}) Y_2^\dagger \quad (7)$$

where

$$C_{Z,1} = \mathbf{X}_1 \mathbf{C}_{A,1} \mathbf{X}_1^\dagger, \quad \mathbf{X}_1 = \begin{bmatrix} 1 & -z_{1,11} \\ 0 & -z_{1,21} \end{bmatrix} \quad (8)$$

where  $z_{1,rc}$  denotes the element on row  $r$  and column  $c$  in matrix  $\mathbf{Z}_1$ . The last deembedding step is then conducted as

$$\mathbf{C}_{A,\text{dut}} = \mathbf{X}_{\text{dut}} (C_{Y,2} - 2kT_f \Re\{\mathbf{Y}_p\}) \mathbf{X}_{\text{dut}}^\dagger \quad (9)$$

$$\mathbf{X}_{\text{dut}} = \begin{bmatrix} 0 & b_{\text{dut}} \\ 1 & d_{\text{dut}} \end{bmatrix} \quad (10)$$

where  $a_{\text{dut}}$ ,  $b_{\text{dut}}$ ,  $c_{\text{dut}}$ , and  $d_{\text{dut}}$  denote the elements of the DUT  $ABCD$  matrix  $\mathbf{A}_{\text{dut}}$ . We may then calculate the DUT noise parameters as [6]

$$Y_{\text{SOF}} = \sqrt{\frac{C_{A,22}}{C_{A,11}} - \left(\frac{\Im\{C_{A,12}\}}{C_{A,11}}\right)^2} + j \left(\frac{\Im\{C_{A,12}\}}{C_{A,11}}\right) \quad (11)$$

$$F_{\min} = 1 + \frac{1}{kT_0} (C_{A,12} + C_{A,11} Y_{\text{SOF}}^*) \quad (12)$$

$$R_n = \frac{C_{A,11}}{2kT_0} \quad (13)$$

which is the desired result. The method may easily be expanded to asymmetrical test fixtures by denoting input and output fixture parasitics separately. Also note that, for shield-based test fixtures, where we may often disregard the parasitics  $Z_f$  and  $Z_s$ , the last two steps of the deembedding algorithm are greatly simplified.

### III. REDUCED COMPLEXITY DEEMBEDDING (RCD)

As noted from the previous section, only the resistive effects of the test fixture are important to the noise correlation matrices. As mentioned previously, the shield-based fixture design method is an effective way of reducing these series parasitics. Hence, we propose a simple noise deembedding technique, which uses no correction of the noise figure and the equivalent noise resistance. However, we compensate for the reactive effects of the test fixture. The method is detailed as follows.

- 1) Measure the noise parameters ( $NF'_{\min}$ ,  $\Gamma'_{\text{SOF}}$ , and  $R'_n$ ) with a measuring system calibrated to the probe tips.

- 2) Approximate the DUT  $NF_{\min}$  and  $R_n$  by the measured values  $NF'_{\min}$  and  $R'_n$ .

- 3) Measure the total input admittance of an open test fixture ( $Y_{\text{open}}$ ) and estimate the optimum source reflection as

$$\hat{\Gamma}_{\text{SOF}} = \frac{2\Gamma'_{\text{SOF}} - Y_{\text{open}}Z_0(1 + \Gamma'_{\text{SOF}})}{2 + Y_{\text{open}}Z_0(1 + \Gamma'_{\text{SOF}})} \quad (14)$$

where  $Z_0$  is the calibration reference impedance.

Hence, the approach requires the fabrication of the test fixture containing the DUT and an additional “open” test fixture. The latter may be obtained simply by separating the DUT from the test fixture using a laser, which may completely alleviate the need for an additional test structure. Although the laser trimming may introduce deembedding imperfections, this effect may be cancelled by the fact that it is the actual test fixture upon which deembedding measurements are being conducted (no tolerances are present).

### IV. EXPERIMENTAL VERIFICATION

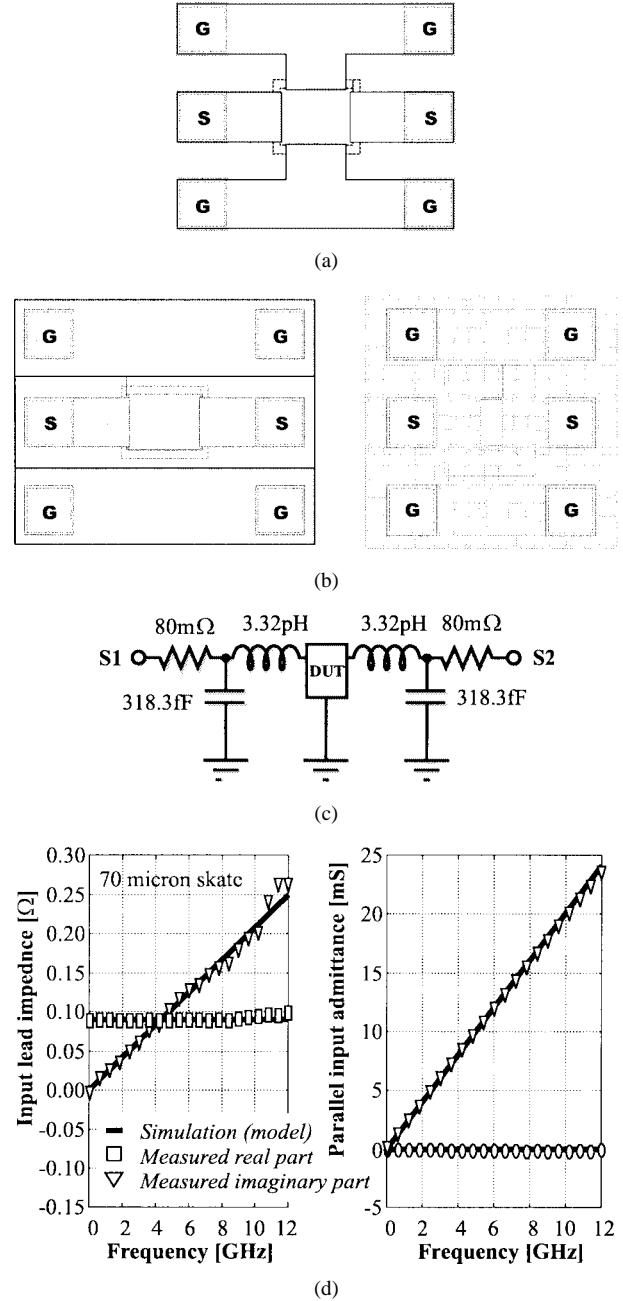

To verify the proposed deembedding method, we have fabricated several test fixtures and devices in standard CMOS silicon technologies employing  $10\text{-}\Omega \cdot \text{cm}$  substrates. The measurements kit includes deembedding standards needed to conduct the full-scale four-step deembedding method [2], also including the open deembedding standard. The kits are available for a conventional test fixture, as well as a shield-based test fixture (example fixtures are given in Fig. 3). An extracted equivalent model for a typical shielded test fixture is illustrated in Fig. 3(b) with comparison to actual measurements in Fig. 3(d).

Further, the kits include MOSFET devices mounted for two-port measurements in the common-source configuration. The method of verification has been as follows.

- 1) Using  $S$ -parameter measurements on the deembedding standards extract, an equivalent model at all relevant frequencies for the raw test fixtures (conventional, as well as shield-based) was extracted, e.g., [9].

- 2) Noise measurements were conducted on the DUT at various frequencies and the noise parameters for the DUT with the test fixture extracted.

- 3) Using the extracted test-fixture model, as well as the noise measurement results, the intrinsic DUT noise

Fig. 3. Illustration of: (a) conventional and (b) shield-based test fixtures used in this study. In (c), a typical model for a shield-based test fixture is shown with comparison to its measured response in (d). All test fixtures employ a  $150\text{-}\mu\text{m}$  pad-pad spacing. Other implementation details can be found in [1] and [9].

parameters are extracted using the two noise deembedding methods outlined earlier. The measurement setup includes a vector network analyzer, a probe station mounted with ground–signal–ground microwave probes, as well as impedance tuners for reporting the noise parameters at various source settings.

The raw noise measurements of the DUT including a test fixture, as well as the deembedded results using the FSD and RSD methods, are listed in Table I for various scenarios (two different RF-optimized MOSFETs in two different CMOS technologies). We shall assume the FSD results to serve as a reasonable reference, as this method uses an accurately extracted

TABLE I

NOISE PARAMETERS FOR THE DUT WITH A TEST FIXTURE, DUT ESTIMATED WITH FSD, AND DUT ESTIMATED WITH RSD. MEASUREMENTS WITH A CONVENTIONAL TEST FIXTURE ARE DENOTED BY "CNV," WHILE MEASUREMENTS WITH A SHIELD-BASED TEST FIXTURE ARE DENOTED BY "SHL"

| NMOS<br>DUT              | Fixt.<br>type | Raw measurement    |                       |                           | FSD                |                       |                           | RSD                |                       |                           |

|--------------------------|---------------|--------------------|-----------------------|---------------------------|--------------------|-----------------------|---------------------------|--------------------|-----------------------|---------------------------|

|                          |               | $NF_{min}$<br>[dB] | $R_n$<br>[ $\Omega$ ] | $\Gamma_{SOF}$<br>[-,deg] | $NF_{min}$<br>[dB] | $R_n$<br>[ $\Omega$ ] | $\Gamma_{SOF}$<br>[-,deg] | $NF_{min}$<br>[dB] | $R_n$<br>[ $\Omega$ ] | $\Gamma_{SOF}$<br>[-,deg] |

| 300x0.5 $\mu$ m, 1.6GHz  | Cnv.          | 1.27               | 75.8                  | 0.799 $\angle$ 44.5°      | 1.05               | 76.0                  | 0.810 $\angle$ 33.0°      | 1.27               | 75.8                  | 0.780 $\angle$ 34.3°      |

| 300x0.5 $\mu$ m, 1.6GHz  | Shl.          | 1.08               | 75.8                  | 0.816 $\angle$ 43.4°      | 1.05               | 75.9                  | 0.811 $\angle$ 33.0°      | 1.08               | 75.8                  | 0.806 $\angle$ 33.1°      |

| 400x0.25 $\mu$ m, 1.6GHz | Shl.          | 0.57               | 20.0                  | 0.639 $\angle$ 60.9°      | 0.54               | 19.6                  | 0.722 $\angle$ 30.7°      | 0.57               | 20.0                  | 0.713 $\angle$ 30.8°      |

| 400x0.25 $\mu$ m, 2.1GHz | Shl.          | 0.76               | 18.0                  | 0.639 $\angle$ 60.9°      | 0.70               | 17.6                  | 0.637 $\angle$ 54.6°      | 0.76               | 18.0                  | 0.623 $\angle$ 54.8°      |

| 400x0.25 $\mu$ m, 2.7GHz | Shl.          | 0.86               | 17.5                  | 0.640 $\angle$ 71.2°      | 0.78               | 17.1                  | 0.633 $\angle$ 63.8°      | 0.86               | 17.5                  | 0.617 $\angle$ 64.3°      |

Measuring temperature is 25°C.

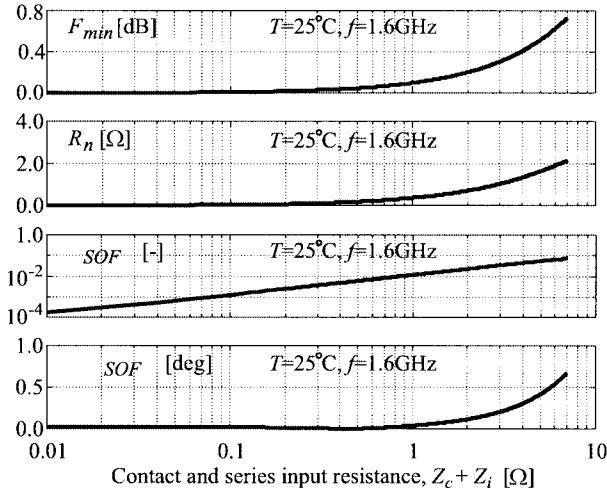

Fig. 4. Impact of series effects on noise parameters of 300  $\times$  0.5  $\mu$ m NMOS. For the given case, we assume  $\Im\{Z_c + Z_i\} = 1.4\Re\{Z_c + Z_i\}$ .

test-fixture model and a proven deembedding technique. Generally, the influence of the shield-based fixture on  $NF_{min}$  is very small with distortion of only 0.03, 0.06, and 0.08 dB at 1.6, 2.1, and 2.7 GHz, respectively. This is close to the specified measuring uncertainty of our system. In comparison, the conventional fixture leads to a rise in  $NF_{min}$  of 0.22 dB at 1.6 GHz. The influence on  $R_n$  is, in both cases, small. For both test fixtures, it is observed that  $|\Gamma_{SOF}|$  is only slightly affected, while  $\angle\Gamma_{SOF}$  is affected considerably.

For the shield-based test fixtures, the proposed one-step deembedding method (i.e., RSD) effectively estimates the device  $\Gamma_{SOF}$ . It is, however, interesting to note that, in some cases, the raw measured reflection  $|\Gamma'_{SOF}|$  is closer to the device  $|\Gamma_{SOF}|$  than the deembedded reflection  $|\hat{\Gamma}_{SOF}|$ . This is caused by two counteracting effects, i.e., a reduction of  $|\Gamma_{SOF}|$  due to the parallel admittance of the fixture and an increase of  $|\Gamma_{SOF}|$  due to thermal noise generated in the input series parasitics. The proposed method compensates only for the parallel admittance and, thus, slightly underestimates  $|\Gamma_{SOF}|$ .

The sensitivity of the proposed deembedding method (i.e., RSD) versus the value of the input series effects  $Z_c + Z_i$  is plotted in Fig. 4. If the series effects are kept well below 1  $\Omega$ , the impact on the noise parameters is typically negligible. This requirement can be fulfilled in most silicon processes, even when including the contact resistance between probes and aluminum metallization.

## V. CONCLUSIONS

In this paper, we have derived an FSD technique compatible with the four-step deembedding model. Further, a simple one-step correction procedure has been proposed for device noise measurements utilizing shield-based test fixtures. Correction is applied for the parallel test-fixture admittance, which is easily estimated with an additional open test fixture. When input series parasitics of the test fixture are kept well below 1  $\Omega$ , measuring errors on the noise parameters are close to the overall measuring uncertainty. Using the simple one-step method, one can expect typical noise-figure accuracy better than 0.05 dB and a noise-resistance accuracy better than 0.1–0.2  $\Omega$ . For more critical cases, e.g., when device noise is very low or the measuring frequency is very high, a full deembedding method should be used. This requires an additional fully shorted test dummy structure. Due to low noise contribution of the shield-based test fixture, the measuring accuracy is generally improved over conventional fixtures. For more critical cases, e.g., when device noise is very low or the measuring frequency is very high, a full deembedding method can be used.

## REFERENCES

- [1] T. E. Kolding, O. K. Jensen, and T. Larsen, "Ground-shielded measuring technique for accurate on-wafer characterization of RF CMOS devices," in *Proc. IEEE Int. Microelectron. Test Structures Conf.*, Monterey, CA, March 2000, pp. 106–111.

- [2] T. E. Kolding, "A four-step method for de-embedding gigahertz on-wafer CMOS measurements," *IEEE Trans. Electron Devices*, vol. 47, pp. 734–740, Apr. 2000.

- [3] M. J. Deen and C.-H. Chen, "The impact of noise parameter de-embedding on the high-frequency noise modeling of MOSFETs," in *Proc. IEEE Int. Microelectron. Test Structures Conf.*, Göteborg, Sweden, Mar. 1999, pp. 34–39.

- [4] C. E. Biber, M. L. Schmatz, T. Morf, U. Lott, E. Morifuji, and W. Bächtold, "Technology independent degradation of minimum noise figure due to pad parasitics," in *IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 1, Baltimore, MD, June 1998, pp. 145–148.

- [5] H. Hillbrand and P. H. Russer, "An efficient method for computer aided noise analysis of linear amplifier networks," *IEEE Trans. Circuits Syst.*, vol. CAS-23, pp. 235–238, Apr. 1976.

- [6] J. Engberg and T. Larsen, *Noise Theory of Linear and Nonlinear Circuits*. New York: Wiley, 1995.

- [7] J. B. Fraleigh and R. A. Beauregard, *Linear Algebra*, 2nd ed. Reading, MA: Addison-Wesley, 1990.

- [8] D. M. Pozar, *Microwave Engineering*. Reading, MA: Addison-Wesley, 1990.

- [9] T. E. Kolding, "Shield-based microwave on-wafer device measurements," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 1039–1044, June 2001.

**Troels Emil Kolding** (S'96–A'99–M'02) received the M.Sc. and Ph.D. degrees in communications and electrical engineering from Aalborg University, Aalborg, Denmark, in 1996 and 1999, respectively.

From 1999 to 2001, he was an Integrated Circuit Design Manager with the RF Integrated Systems and Circuits Group, Aalborg, Denmark, where he managed the design and fabrication of an RF CMOS direct conversion WCDMA receiver for the UMTS system. In 2001, he joined Nokia Networks, Aalborg, Denmark, where he leads a research program related to high-speed data concepts for 3.5G wireless networks. He conducts advanced on-wafer measuring training of both industry and academia. His current research interests include on-wafer measuring techniques, device modeling, integrated circuit (IC)/systems design, as well as WCDMA techniques.

Dr. Kolding is a reviewer for the IEEE.

**Christian Rye Iversen** received the M.Sc.E.E. and Ph.D. degrees from Aalborg University, Aalborg, Denmark, in 1995 and 2002 respectively. His Ph.D. research concerned RF-CMOS low-noise amplifier design.

From 1995 to 1997, he designed digital enhanced cordless technology (DECT) RF circuits with Cordless Technology, Pandrup, Denmark. In 1997, he was an RF Design Engineer with Siemens Mobile Phones, Pandrup, Denmark. In 1998, he joined the RF Integrated Systems and Circuits Group. Since 2002, he has been with RF Micro Devices, Pandrup, Denmark. His current research interests include RF CMOS circuit design, integrated device modeling, and highly integrated transceivers for wireless systems.